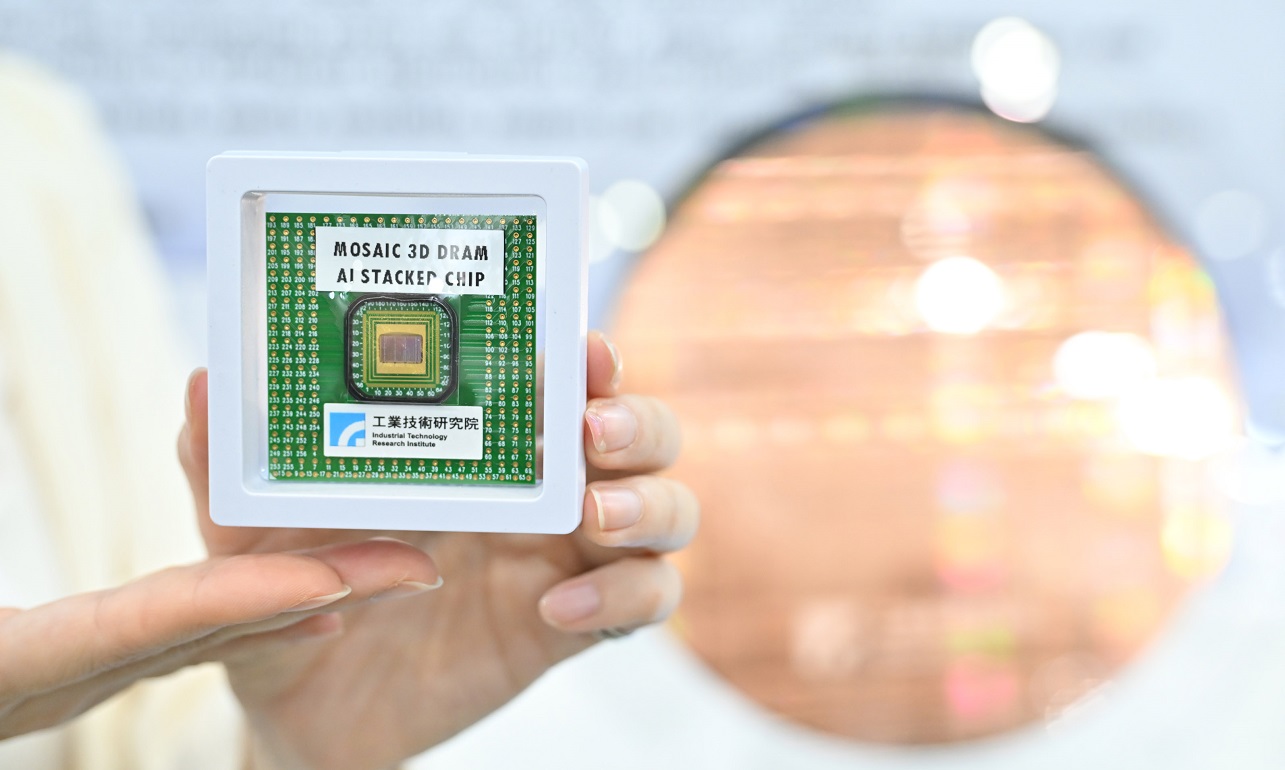

全球掀起AI大浪,對高頻寬記憶體的需求也急速增長。工研院積極投入半導體前瞻技術,開發出將邏輯運算和記憶體整合在一起的「MOSAIC 3D AI 晶片」,以創新的3D堆疊技術,運算及記憶體彈性管理,推動晶片設計與製造技術革新,確保臺灣在這場國際AI競賽中保持領先地位,榮獲2024全球百大科技研發獎。

AI浪潮勢不可擋,隨著AI處理器性能提升,對於提供高算力和大頻寬的高速記憶體需求也愈來愈迫切。能提供更高頻寬的「高頻寬記憶體」(HBM),成了市場當紅炸子雞,但因製作工序複雜且價格高貴,僅限用於高階伺服器產品,也因需求激增,面臨供不應求的局面。

為了解決這個難題,工研院與力積電攜手研發將邏輯運算和記憶體整合在一起的「MOSAIC 3D AI 晶片」,藉由可彈性延伸的3D堆疊技術,使晶片間的傳輸距離從微米大幅縮短至奈米,產生的熱能也僅十分之一,成本也僅五分之一,提供AI產業更高效能、高彈性、高CP值的替代方案。

首創3D堆疊方式 彈性組合記憶體

MOSAIC其實就是大家熟悉的「馬賽克」,工研院電子與光電系統研究所經理羅賢君笑稱,主要是該技術的動態隨機存取記憶體(DRAM)可以根據晶圓大小和廠商需求任意堆疊組合,像馬賽克一樣可以自由拼貼而得名。

羅賢君解釋,過去DRAM都是一大片固定尺寸進行封裝,「這個技術把它化整為零,將DRAM切分成一小塊、一小塊,每一塊就代表一個DRAM單位。」切分成一小塊的好處是,第一容量可以變大,晶圓有多大,就可以組裝多大的記憶體;第二資料傳輸速度可以變快,假設拼了4塊,速度就變4倍,拼了8塊就變8倍,數量愈多傳得愈快。

團隊的創舉不只是讓DRAM可以自由堆疊,還提出獨特的3D結構。羅賢君指出,現有的HBM結構可看作是平面連接,當CPU要和HBM進行快速大量的資料傳輸時,必須先把資料從HBM傳到載板,再從載板的線路通道傳到CPU。

但工研院的解法是,運用3D堆疊的立體方式,直接把DRAM記憶體架在CPU上,由上往下就可以傳輸資料,羅賢君比喻,「就像搭電梯,資料直接下到1樓的CPU,不需要經過載板通道。」此舉不僅將晶片的傳輸距離從微米大幅縮短到奈米,還能用便宜的DDR1的記憶體,達到如同DDR4甚至DDR5的傳輸速度。

也因為3D堆疊,資料傳輸通道的數量更多,比起HBM連線通道約1,000~2,000個,MOSAIC 3D AI 晶片可多達1、2萬個,顯著提升資料傳輸頻寬;而3D堆疊也讓整個晶片的體積縮小,大幅縮短運算核心,連帶讓中間傳輸的耗能大幅降低。而HBM因為技術難度高,成本高昂,MOSAIC 3D AI 晶片可大幅降低成本,僅需五分之一即可。

克服資料存取關卡 支援各種AI場景

雖然將DRAM切分成一小塊的優點不少,但也帶來新的技術關卡。羅賢君指出,發展成熟的DRAM產業,有行之已久的JEDEC標準,所有DRAM都要符合這個標準才行,但切分成小塊就會面臨到新的界面定義,以及新的電路和管理系統,這是團隊面臨的最大難題。

由於資料龐雜,1、2萬個資料傳輸通道都必須集中處理,需要一個新的控制器,才能符合新的DRAM特殊規格架構,於是團隊打造了數個階層控制器,先收集處理DRAM的資料,再傳輸到CPU的大控制上。簡單來說,如果拼了9塊,就會有9個小控制器,再加上一個CPU的大控制器。

控制器也會面臨訊號同步的問題,羅賢君比喻,就像10個人跳舞,每個人的動作都要一樣才行。要做到晶片同步,需要分區切割、緩衝處理、資料預測、資料暫存等技術,團隊克服這些資料存取的關卡,才能讓控制器如常運作。

不只在晶片設計上,這項技術在製程上也有突破,由力積電負責一條龍組裝,將邏輯運算與DRAM記憶體交由同一家廠商代工整合、堆疊的製造模式,打破業界現行需交由不同廠商負責的模式,客戶也可以自備邏輯運算,由力積電整合,提供多層DRAM堆疊,客製化程度高,提供3D晶片一條龍的服務,目前已獲國際晶片大廠青睞。

這項技術具有模組化、多階層、易延展的特性,未來可支援各種AI應用場景,不管是小型的穿戴式裝置、攜帶式終端,或是高效能運算(HPC)伺服器、大型雲端運算系統,滿足AI遍地開花的需求,「這項技術扮演一個承先啟後的角色,會對AI發展帶來非常重要的轉變!」

羅賢君認為,當HBM一片難求時,這項技術可以為許多,資源有限卻想投入AI晶片的中小型廠商,提供一個替代的解套方法。未來3D堆疊一定是趨勢,也能幫助廠商先布局,率先試產相關產品,為將來的主流市場鋪路,「帶動臺灣半導體產業一起升級」。

(本文由工業技術與資訊授權轉載)